When AMD started to design Bobcat back in 2005 - 2006, it already knew that its K7/K8/K9 chips were too power hungry for mobile computers, whereas the preceding generations were too inefficient in modern workloads. As a result, the company decided to design the chip from scratch rather than to "borrow" designs from previous-generation products. However, AMD decided not to sacrifice performance in order to absolutely minimize power consumption. As a result, Bobcat seems to be almost completely contemporary chips with numerous design trade-offs to reduce power consumption. According to AMD, the micro-architecture minimizes data movement and unnecessary reads from cache or memory.

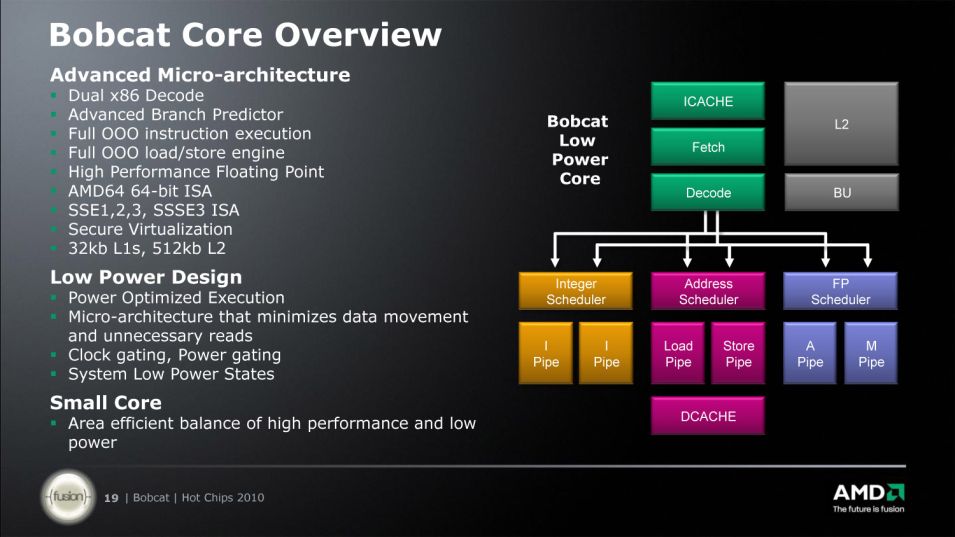

The Bobcat core sports out-of-order execution, advanced branch predictor, dual x86 instruction decoder, 64-bit integer unit with two ALUs, floating point unit with two 64-bit pipes, 32KB instruction cache, 32KB data cache, 512KB L2 cache (working at half speed to trim power consumption) and so on. Bobcat fully supports modern SIMD extensions like SSE, SSE2, SSE3, SSSE3, SSE4A, but no 3DNow, AVX and so on. AMD Bobcat features an extensive set of means to reduce power consumption, including such capabilities as fine grain clock gating, integrated core power gating and so on.

The first implementation of Bobcat will be Ontario chip that features one or two x86 processing cores as well as DirectX 11 graphics processing unit from ATI. The chip will be made using 40nm process technology at TSMC and will be released commercially in Q1 2011.

No comments:

Post a Comment